# Estratetegia de Control *Droop* con Reducido Número de Sensores Para Inversores en Paralelo en UPS

Roberto E. Carballo #1, Fernando Botterón \*, Germán G. Oggier #, Guillermo O. García #

# Grupo de Electrónica Aplicada, CONICET, Universidad Nacional de Río Cuarto Ruta Nacional #36 km 601, Río Cuarto, Cordobá, Argentina

<sup>1</sup> carballore@gmail.com

\* Grupo de Investigación y Desarrollo en Ingeniería Electrónica, CONICET, Universidad Nacional de Misiones Juan Manuel de Rosas 325, Oberá, Misiones, Argentina

Abstract — A droop control strategy is proposed to achieve parallel operation of single-phase inverters for double conversion UPS applications. The distinctive caracteristics of this control strategy are a reduced number of sensors to achieve output impedance adjustment, fixed frequency of the output voltage, reduced circulating current between the inverters, excelent output voltage regulation and compliance with specifications given by international standards for transient and stationary response. A simple design methodology is proposed to choose the droop controller gain and adjust the output impedance value of each inverter, validating the proposal with simulation results.

Resumen —Se propone una estrategia de control droop para la conexión de inversores monofásicos en paralelo utilizados en UPS de doble conversión. Esta estrategia logra una reducida cantidad de sensores para el ajuste de la impedancia de salida, operación con frecuencia fija de la tensión de salida, reducida corriente de circulación, excelente regulación, y cumple con las especificaciones de desempeño transitorio y de régimen permanente establecidas por normas internacionales. Se propone una metodología simple para la selección de la ganancia del controlador droop y el ajuste del valor de la impedancia de salida para cada inversor, validando la propuesta con resultados de simulación.

## I. INTRODUCCIÓN

La operación en paralelo de inversores es utilizada principalmente para lograr repartir entre un número de convertidores la potencia demandada por una carga.

Las fuentes de alimentación ininterrumpidas (UPS – *Uninterruptible Power Supplies*) compuestas por inversores conectados en paralelo logran sistemas con elevada confiabilidad y disponibilidad de energía eléctrica. Por otro lado, debido a la reducida impedancia de salida que poseen los inversores de altas prestaciones [1], la conexión en paralelo puede causar circulación de corrientes entre estos [2], siendo cualquier diferencia entre los parámetros de los filtros *LC*, los controladores y sensores utilizados lo que produce una diferencia en las impedancias de salida y el consecuente desequilibrio en las corrientes entregadas por cada unidad.

Las estrategias para mitigar este problema pueden clasificarse en dos grupos [3]: las que utilizan comunicación de datos entre los convertidores y las que no utilizan comunicación.

Debido a que la utilización de comunicación de datos requiere de hardware adicional e introduce puntos de falla que pueden quitar de operación a todo el sistema, las estrategias de control que no utilizan comunicación suelen ser las más elegidas, sobre todo cuando la distancia que separa a los inversores es considerable. Como desventaja, debido a que la estrategia de control requiere incrementar la impedancia de salida para disminuir la corriente de circulación, la regulación de la tensión en la carga resulta comprometida. Las estrategias de control sin comunicación funcionan a partir de la medición de señales disponibles en los terminales de salida del inversor, implementándose en cada convertidor el control que permite la operación en paralelo. Como sub clasificación para estas estrategias se puede mencionar el control *droop* [4, 5], emulación de generadores síncronos [6], y osciladores no lineales [7].

De estas estrategias, el control *droop* presenta menor complejidad de diseño e implementación. Basado en el principio de funcionamiento de generadores síncronos en paralelo que conforman el sistema eléctrico de potencia, estas estrategias proponen introducir una característica de caída en la frecuencia en función de la potencia activa entregada por el inversor, introduciendo de esta forma la relación entre potencia activa y el ángulo de potencia que permite obtener un funcionamiento sincrónico entre todos los inversores [8].

Las características de fase de las impedancias que interconectan a los inversores, determinan el mecanismo de transferencia de potencia entre estos, y consecuentemente el algoritmo de *droop* correspondiente a esta característica [9]. Para evitar introducir estas impedancias las cuales aumentan el costo y volumen del sistema, diversos trabajos proponen emular la impedancia de salida del inversor utilizando el sistema de control de cada convertidor [10, 11].

La emulación de la impedancia de salida requiere generalmente de la realimentación de la corriente de salida, la cual corresponde a la corriente medida después del filtro LC utilizado típicamente en estos inversores. A partir de esta medición se implementa un lazo de impedancia virtual que establece la característica de la impedancia tanto en magnitud como en fase, pudiéndose realizar impedancias inductivas, resistivas, capacitivas o complejas [9].

Teniendo en cuenta que es posible modificar la impedancia de salida a partir de los lazos de realimentación de tensión del capacitor y corriente del inductor, es posible eliminar el sensor de corriente de salida. Este hecho ha sido señalado en [12], y los autores propusieron implementar el lazo de impedancia virtual a partir de la corriente del inductor.

Considerando que los controladores *droop* estructuralmente coinciden con los PLL (*phased locked loop* – lazo de enganche de fase) [13], en [14] se propone utilizar el SRF-PLL (*synchronous reference frame* – PLL) junto con un lazo de impedancia virtual resistiva, lo cual se puede demostrar que es equivalente a utilizar solamente la potencia reactiva en el controlador *droop* clásico, reduciéndose consecuentemente el costo computacional del algoritmo de control.

Para operar los inversores con frecuencia fija, la propuesta [15] realiza el *droop* directamente sobre el ángulo en lugar de la frecuencia. Esta característica es muy importante para el caso de UPS de doble conversión, siendo preferible una tensión de salida con frecuencia prácticamente constante.

En función de los conceptos mencionados hasta aquí, en este trabajo se propone una estrategia de control droop que presenta tres características distintivas en comparación con las propuestas anteriores: i) utiliza solamente la potencia activa en el algoritmo de droop, ii) la impedancia de salida presenta una característica predominantemente inductiva a frecuencia fundamental, implementándose el lazo de impedancia virtual directamente a partir de realimentación de la corriente del inductor, y iii) al combinar el lazo de impedancia virtual con los controladores resonantes propuestos en [16], la impedancia de salida en las frecuencias armónicas de la fundamental presenta características resistivas con valores muy reducidos, con lo cual se logra que la tensión de salida cumpla con las normas internacionales para UPS y sistemas de distribución de baja tensión [16].

Además, se propone un esquema para implementar el controlador *droop* de ángulo con el objetivo de mantener una tensión de salida con frecuencia constante y evitar la degradación de las características de rechazo de perturbaciones de los controladores resonantes.

## II. ESTRATEGIA DE CONTROL

## A. Descripción del modelo de la planta y de la estrategia de control

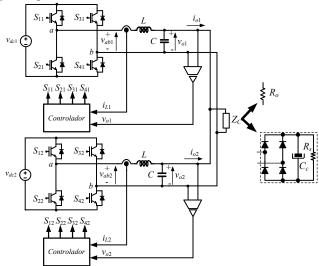

En la Fig. 1 se muestra la conexión en paralelo de los inversores monofásicos considerados en el desarrollo de este trabajo, donde la planta para cada inversor estará definida a partir de las dinámicas del filtro LC de salida.

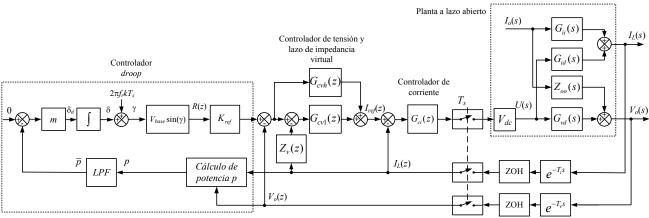

En la Fig. 2 se presenta el diagrama de bloques que describe la estrategia de control de múltiples lazos de realimentación implementada en cada inversor, incluyendo los efectos de la implementación digital a partir del modelo de pequeña señal de la planta, según se propuso en [17].

Los bloques que representan a las funciones de transferencia de la planta en la Fig. 2 corresponden a  $G_{vd}(s)$ , la cual relaciona la tensión de salida  $V_o(s)$  respecto de la tensión a bornes del puente de semiconductores de potencia U(s), y  $G_{id}(s)$  relaciona la corriente del inductor  $I_L(s)$  respecto de U(s). Por otro lado,  $Z_{oo}(s)$  es la función de transferencia que relaciona la tensión de salida con la corriente de salida, considerada como perturbación del sistema, por lo que  $Z_{oo}(s)$  es la impedancia de salida del sistema a lazo abierto, y  $G_{ii}(s)$  es la función de transferencia que relaciona la corriente del inductor con la corriente de carga. Todas estas funciones de transferencia dependen de

los parámetros del filtro LC, pudiéndose encontrar las expresiones matemáticas correspondientes en [16]. Los atrasos de transporte mostrados en el diagrama de bloques de la Fig. 2, representan los retardos de tiempo ocurridos entre los instantes en los que se realiza el muestreo y se actualiza la acción de control para los distintos lazos de realimentación, los que vienen dados por  $T_i$  y  $T_v$ , considerándose en este trabajo  $T_i = T_v = T_d$ , siendo  $T_d = T_s/2$  y  $T_s$  el periodo de muestreo.

Fig. 1. Inversores monofásicos conectados en paralelo, cargas típicas y variables utilizadas en la estrategia de control.

La discretización de las funciones  $G_{id}(s)$  y  $G_{vd}(s)$  se realizan aplicando la transformada z modificada [17], contemplándose los retardos de tiempo  $T_d$  debidos a la implementación digital, mientras que las funciones  $G_{ii}(s)$  y  $Z_{oo}(s)$  se discretizan utilizando la transformada de Tustin con pre-wrapping, siendo la frecuencia de resonancia del filtro LC utilizada para corregir la deformación.

El controlador del lazo interno de control de corriente presentado en la Fig. 2.  $G_{ci}(z)$ , corresponde a una ganancia proporcional que se diseña para maximizar el amortiguamiento activo de los polos de la planta, considerando los parámetros nominales del sistema dados en la Tabla I [16].

El bloque  $G_{cv1}(z)$  de la Fig. 2 corresponde a la función de transferencia del controlador resonante a frecuencia fundamental

$$G_{cv1}(z) = \text{FOH}\left\{K_{r1} \frac{s\cos(\theta_1) - \omega_1 \sin(\theta_1)}{s^2 + \omega_1^2}\right\},\tag{1}$$

mientras que  $G_{cvh}(z)$  son los múltiples controladores resonantes en las frecuencias armónicas de la fundamental

$$G_{cvh}(z) = \sum_{i=3}^{n} \text{FOH}\left\{K_{ri} \frac{s\cos(\theta_i) - \omega_i \sin(\theta_i)}{s^2 + \omega_i^2}\right\},$$

(2)

Como se puede observar, la función de transferencia discreta se obtiene a partir de aplicar la discretización por retenedor de primer orden (FOH - *first order hold*), la cual permite obtener una aproximación más precisa sin causar corrimiento de la frecuencia de resonancia y de la característica de fase del controlador [18]. Los parámetros de cada controlador resonante vienen dados por: la ganancia  $K_{ri}$ , la frecuencia angular de resonancia  $\omega_i$ , y el ángulo de compensación  $\theta_i$  [19].

Fig. 2. Diagrama de bloques de la estrategia de control de cada inversor de la Fig. 1

La separación de los múltiples controladores resonantes en dos bloques tiene como objetivo que la acción de la impedancia virtual tenga efecto solamente sobre la señal de error del controlador resonante a frecuencia fundamental, con lo cual se logra incrementar la impedancia de salida solamente a esta frecuencia. Esto marca una diferencia significativa con la propuesta [20], donde la impedancia virtual actúa en la señal de error del lazo externo de control de tensión, causando la pérdida de rechazo a perturbaciones periódicas al incrementarse la impedancia de salida en cada frecuencia armónica de los controladores resonantes.

En función de la metodología aplicada para el diseño del controlador en el lazo externo de control de tensión [16], los controladores resonantes a introducir corresponden a la frecuencia fundamental, 3<sup>ra</sup>, 5<sup>ta</sup>, 7<sup>ma</sup>, 9<sup>na</sup>, 15<sup>ta</sup>, 21<sup>ra</sup> y 27<sup>ma</sup> armónicas de la fundamental.

Tabla I

Parámetros de cada Inversor monofásico de la Fig. 1

| Potencia de salida, S                                          | 1 kVA   |

|----------------------------------------------------------------|---------|

| Tensión de entrada, $V_{dc}$                                   | 400 V   |

| Tensión de salida, $V_{ac\text{-}RMS}$                         | 220 V   |

| Frecuencia fundamental, $f_r$                                  | 50 Hz   |

| $Valor\ base\ de\ corriente,\ I_{base}$                        | 6,43 A  |

| $Valor\ base\ de\ tensión,\ V_{base}$                          | 311 V   |

| Valor de impedancia base, $Z_{base}$                           | 48,36 Ω |

| Frecuencia de muestreo y conmutación, f <sub>s</sub>           | 10 kHz  |

| Inductancia filtro de salida, L                                | 500 μΗ  |

| Resistencia del inductor $L$ , $r_L$                           | 0,118 Ω |

| Capacitancia filtro de salida, C                               | 60 μF   |

| Resistencia de carga nominal total, R <sub>c</sub>             | 24,18 Ω |

| Resistencia de la carga no lineal, $R_s$                       | 48,4 Ω  |

| Resistencia de suavizado de la carga no lineal, R <sub>1</sub> | 0,97 Ω  |

| Capacitancia de la carga no lineal, $C_c$                      | 3300 μF |

La función de la ganancia  $K_{ref}$  que se observa en la Fig. 2 se utiliza para compensar el efecto de la impedancia de virtual sobre la regulación de tensión en la condición de vacío, detallándose su cálculo más adelante en esta sección.

El cálculo del argumento  $\gamma$  de la señal de referencia para cada convertidor se realiza a partir del controlador droop, utilizando el esquema que permite implementar la relación P- $\delta$ , con la cual se logra evitar variaciones de frecuencia en el sistema [15]. La ganancia m en la Fig. 2 corresponde a la pendiente de la recta P- $\delta_d$ , siendo  $\delta_d$  la cantidad en la que se reduce el ángulo cuando aumenta la potencia activa media, debiendo integrarse esta variable en el tiempo para obtener el ángulo  $\delta$ , el cual se suma finalmente al argumento

calculado en cada periodo de muestreo  $2\pi f_r kT_s$ , con lo cual el argumento de la señal de referencia viene dado por

$$\gamma = 2\pi f_r k T_s + \delta \tag{3}$$

donde k es el índice de iteración que se incrementa en cada periodo de muestreo, comenzando de 0 hasta llegar a  $f_s/f_r$ , para luego reiniciarlo.

Por último, el bloque *FPB* corresponde al filtro pasa bajos utilizado para eliminar la componente oscilante de la potencia activa instantánea *p*, la cual se calcula utilizando la teoría de la potencia activa instantánea extendida para el caso de sistemas monofásicos [21].

## B. Diseño de los controladores en los lazos internos de control

Para el diseño de los múltiples controladores resonantes, los ángulos de compensación utilizados para corregir el atraso de fase introducido por la planta en el sistema a lazo cerrado, se determinan a partir de la característica de fase del sistema comprendido por la planta con el lazo interno de control de corriente con ganancia proporcional [16].

Para la ganancia del controlador resonante a frecuencia fundamental, esta se determina para cumplir con la respuesta transitoria de la tensión de salida especificada para el caso de realizarse variaciones de carga lineal del tipo escalón [16]. En cuanto a las ganancias para los controladores resonantes a frecuencias armónicas de la fundamental, la metodología de diseño propuesta en [16] permite definir la impedancia de salida en cada armónica de manera tal de cumplir con los límites del contenido armónico individual de la tensión de salida cuando se alimenta una carga no lineal de referencia, estando esta carga especificada en la norma IEC 62040-3.

Los múltiples controladores resonantes utilizados en el lazo externo de control de tensión, reducen significativamente la impedancia de salida del inversor en la frecuencia de cada controlador resonante. Una reducida impedancia de salida en la frecuencia fundamental torna al sistema sensible a una circulación de corriente inadmisible entre los inversores, por lo que se propone introducir el lazo de impedancia virtual para ajustar convenientemente la impedancia de salida a esta frecuencia.

### C. Lazo de impedancia virtual

Para realizar una inductancia virtual se requiere de una función de transferencia que genere a su salida una señal ortogonal. De las posibles funciones de transferencia con esta característica [22], se propone utilizar la del filtro pasa todo, por lo que la expresión de la impedancia virtual es

$$Z_{v}(s) = k_{zv}(s + \omega_f)/(s - \omega_f). \tag{4}$$

El filtro pasa todos produce un retardo de fase de  $90^{\circ}$  a la frecuencia  $\omega_f$ . Esta función de transferencia es preferida frente a las otras por su simplicidad de implementación y porque presenta una característica de magnitud constante en todas las frecuencias, lo cual es importante para no amplificar el ruido que puede formar parte de la señal realimentada.

Por lo tanto, la ganancia  $k_{zv}$  en (4) definirá la magnitud de la impedancia de salida y  $\omega_f$  la frecuencia en la que se produce la fase 90°.

Para implementar la forma discreta de la impedancia virtual se discretiza (4) aplicando la transformación bilineal o de Tustin.

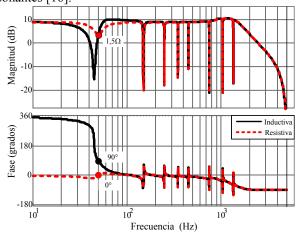

Para observar el efecto de  $Z_v(z)$  sobre la impedancia de salida del inversor, se debe determinar la función de transferencia de la impedancia de salida  $Z_o(z)$  a partir de analizar el diagrama de bloques de la Fig. 2 con R(z) = 0. Evaluando  $Z_o(z)$  con una inductancia virtual de  $1,5\Omega$ , en la Fig. 3 se presenta la respuesta en frecuencia de la impedancia de salida, observándose que a 50Hz la magnitud es de  $1,5\Omega$ , y la fase es de  $90^\circ$ , con lo cual se verifica que la impedancia virtual propuesta impone efectivamente la característica de la impedancia de salida que se quiere lograr a la frecuencia fundamental, mientras que en torno a las frecuencias armónicas, la impedancia de salida mantiene las características de rechazo de perturbación determinada a partir de la metodología de diseño para los controladores resonantes [16].

Fig. 3. Impedancia de salida para dos casos de impedancia virtual, impedancia inductiva en trazo continuo negro, e impedancia resistiva en trazo discontinuo rojo.

Debe notarse que en caso de hacer  $Z_{\nu}(s) = k_{z\nu}$  la impedancia virtual es resistiva pura. En la Fig. 3 se compara la respuesta en frecuencia para este caso con el caso de impedancia virtual inductiva, corroborándose la característica deseada de magnitud y fase a frecuencia fundamental.

A diferencia de los esquemas que implementan el lazo de impedancia virtual a partir de la realimentación de la corriente de salida, al utilizarse la corriente del inductor la acción de  $Z_{\nu}(z)I_L(z)$  observada en la Fig. 2, tendrá un efecto sobre el valor pico de la tensión de salida en estado de

vacío, pudiendo presentarse un valor pico por arriba o por debajo del valor nominal, dependiendo de la característica de fase de la impedancia de salida a frecuencia fundamental.

Para compensar este efecto, se propone implementar una ganancia que escale a la referencia, la cual se observa como  $K_{ref}$  en la Fig. 2, pudiendo calcularse esta ganancia como sigue:

$$K_{ref} = 1/|G_{lc}(e^{j2\pi 50T_s})|,$$

(5)

donde  $G_{lc}(e^{j2\pi 50T_s})$  es la evaluación en la frecuencia fundamental de la función de transferencia del sistema a lazo cerrado  $G_{lc}(z)$ , obteniéndose esta función luego de analizar el diagrama de bloques de la Fig. 2 con  $I_0(z) = 0$ .

Concluido el diseño de los lazos internos de control y presentado el mecanismo de ajuste de la impedancia de salida, a continuación se propone una metodología simple para la selección de la ganancia del controlador *droop* y el valor de la impedancia de salida para disminuir la corriente de circulación entre los inversores.

## D. Metodología de diseño del valor de la impedancia de salida y del controlador droop

Para determinar los valores de la impedancia de salida y la ganancia m del controlador droop, se debe tener en cuenta que estos parámetros influyen en la estabilidad del sistema según lo descrito en [5]. De acuerdo a este trabajo, el aumento de la impedancia de salida contribuye a mejorar la estabilidad, llevando los polos dominantes del sistema hacia la izquierda del plano s, mientras que incrementar m lleva a estos polos a posiciones de menor amortiguamiento, pero no inestabilizan al sistema.

Un análisis más detallado en donde se incluyen las dinámicas de los lazos internos de control se presenta en [23], en donde se muestra que los polos dominantes pueden ser inestables cuando *m* se incrementa por encima de un determinado valor crítico.

Teniendo en cuenta estas consideraciones, se propone una metodología de diseño para estos parámetros utilizando simulaciones numéricas, la cual se puede resumir en los siguientes pasos:

- 1) Implementar los inversores en paralelo con una misma referencia en los lazos de control de tensión y con el sistema alimentando una carga resistiva nominal, ajustar la impedancia virtual para obtener la relación de compromiso deseada entre regulación de tensión y corriente de circulación entre los inversores. Se debe tener en cuenta en la simulación la diferencia paramétrica entre los sensores de tensión de los inversores, siendo este factor el más influyente en la circulación de corriente [24].

- 2) Implementar los inversores en paralelo con controladores *droop* y alimentar una carga resistiva nominal con un inversor, realizar la conexión del segundo inversor para evaluar la dinámica de la corriente de circulación e ir aumentando el valor de *m* en cada simulación hasta obtener la respuesta dinámica deseada.

A partir de los resultados de simulación que se presentan a continuación, se ilustra la aplicación de la metodología de diseño.

#### III. RESULTADOS DE SIMULACIÓN

En esta sección se presentan los resultados de simulación obtenidos con el simulador de circuitos eléctricos PSIM, en el cual se implementaron dos inversores monofásicos con los controladores diseñados en las secciones anteriores.

Para realizar las simulaciones en un simulador de circuitos eléctricos, se debe especificar la diferencia paramétrica que existe entre los dos inversores en paralelo. Para los resultados presentados se utilizó una diferencia del 1% entre las ganancias de los circuitos de medición de tensión, ya que la tolerancia de los componentes que integran a los circuitos de medición puede producir una diferencia dentro de este orden de magnitud [24]. Esto se comprende dado que el TCR (temperature coefficient of resistance — coeficiente de temperatura de la resistencia) de resistores utilizados en estos circuitos puede causar diferencias dentro del 1% respecto de su valor a temperatura ambiente.

Para establecer el valor de la impedancia de salida según se propuso en el primer ítem de la metodología de diseño presentada en la sección anterior, se deben especificar los límites para la regulación de tensión y la corriente de circulación.

Si bien la especificación del valor de regulación dependerá de la aplicación, es posible encontrar en el mercado, UPS de altas prestaciones que cuentan con tecnología para paralelizar inversores con valores del 2% de regulación de tensión, por lo que se considera este valor en el diseño.

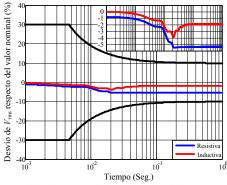

A partir de realizar las simulaciones numéricas se determinó que para obtener una regulación del 2% es necesaria una impedancia de salida de  $3\Omega$ . En la Fig. 4 se presenta el desvío del valor RMS móvil de la tensión sobre la carga cuando se realiza el ensayo de respuesta transitoria ante una entrada escalón de carga lineal, debiendo estar esta variable dentro de las cotas establecidas por la clasificación más exigente de la norma IEC 62040-3. Como se puede observar en la imagen ampliada en el margen superior de la Fig. 4, la regulación de tensión resultante es del 2%.

Fig. 4. Desvío del valor RMS de la tensión de salida respecto del valor nominal para un escalón del 20 al 100% de carga lineal, y cotas establecidas por la clasificación 1 de la norma IEC 62040-3. Imagen ampliada de este resultado para observar la regulación de tensión.

Para comparar la regulación de tensión en el caso de una impedancia virtual resistiva, se realizó la misma simulación con escalón de carga lineal, presentándose el desvío del valor RMS de la tensión de salida en la Fig. 4. En este caso se observa que la regulación de tensión es del 5,5%.

Para obtener la corriente de circulación entre los inversores de la simulación numérica, se define esta variable como

$$i_{cir} = \frac{i_{L1} - i_{L2}}{2} \ . \tag{6}$$

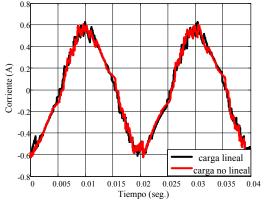

En la Fig. 5 se presenta la corriente de circulación obtenida con la impedancia de salida de  $3\Omega$ . Como se puede observar,  $i_{cir}$  resultó del orden de 600mA, lo cual representa un 9,33% del valor de la corriente de carga nominal entregada por cada inversor. Si se tiene en cuenta que los inversores para aplicaciones de UPS típicamente son diseñados para tener su mayor rendimiento por arriba del 50% de su capacidad de carga, es razonable tolerar un valor en torno al 10% de subutilización de un inversor y sobreutilización del otro.

Fig. 5. Corriente de circulación cuando se alimenta carga lineal y no lineal, nominal.

En cuanto al caso en que se alimenta una carga no lineal, en la Fig. 5 también se presenta la respuesta en régimen permanente de la corriente de circulación para este caso, en la cual se observa que la forma de onda no se modifica significativamente respecto del caso de cuando se alimenta la carga lineal. Esto significa que la diferencia paramétrica entre los sensores de tensión de cada inversor prácticamente no afecta al reparto de corriente armónica, resultado que valida la propuesta realizada de obtener una elevada impedancia de salida en la frecuencia fundamental, y reducida en las armónicas de la fundamental donde la corriente consumida por la carga no lineal de referencia produce distorsión armónica.

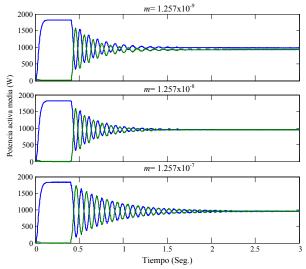

Fig. 6. Potencias activas medias entregadas por cada módulo durante la conexión del segundo inversor para tres valores diferentes de m.

En la Fig. 6 se presentan los resultados obtenidos de las potencias activas medias cuando se realiza la simulación propuesta en el ítem 2) de la metodología de diseño con la impedancia de salida inductiva para tres valores de *m*.

Como se puede observar para el caso de m en el orden de  $10^{-9}$ , la respuesta del controlador droop es lenta permaneciendo una diferencia entre las potencias activas entregadas por cada inversor. Esta diferencia desaparece cuando m es del orden de  $10^{-8}$ , mientras que para m del orden de  $10^{-7}$  se observa un aumento en las oscilaciones de las potencias, lo que indica menor estabilidad relativa del sistema.

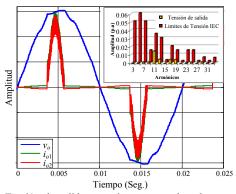

Finalmente, en la Fig. 7 se presenta la respuesta en régimen permanente de la tensión y de las corrientes de salida de cada inversor para el caso de alimentar una carga no lineal. Superpuesta en esta figura se observan el cumplimiento del contenido armónico individual establecidos por la norma IEC 61000-2-2, siendo la  $THD_{\nu}$  de 1,78%.

Es importante resaltar que con el controlador *droop* propuesto se mantiene la frecuencia constante en las señales de referencia para cada inversor, con lo cual los inversores no pierden la característica de rechazo de perturbaciones obtenida con los controladores resonantes.

Fig. 7. Tensión de salida y corriente entregada a la carga por cada inversor alimentando una carga no lineal de referencia. Esc. Tensión 100V/div. Esc. Corriente 5 A/div. THD<sub>v</sub> = 1,78%.

### IV. CONCLUSIONES

En este trabajo, se propuso una estrategia de control *droop* con reducido número de sensores, la cual permite ajustar efectivamente la impedancia de salida a la frecuencia fundamental y obtener una reducida impedancia de salida en las frecuencias armónicas. La metodología de diseño propuesta basada en simulaciones numéricas posibilita seleccionar de forma simple la magnitud de la impedancia de salida y la ganancia *m* del controlador *droop*, con el objetivo de disminuir a valores operativos la circulación de corriente entre los inversores.

De los resultados de simulación presentados se concluye que la regulación de tensión es mejor en casos de impedancias de salida fuertemente inductivas. Además, gracias a la característica P- $\delta$  del controlador droop propuesto, la frecuencia en el sistema permanece constante, con lo cual el rechazo de perturbaciones logrado por los controladores resonantes en los lazos internos de control consigue el cumplimiento de las normas, siendo estas características significativas en UPS de doble conversión.

#### **AGRADECIMIENTOS**

El presente trabajo es financiado por la Secretaría de Ciencia y Técnica de la Universidad Nacional de Río Cuarto (SeCyT, UNRC), Programa Agrovalor I de la FI-UNAM, el FONCyT y el Ministerio de Industria y Desarrollo Científico Tecnológico de la provincia de Córdoba (MICMDCT, Cba).

#### REFERENCIAS

- M. J. Ryan, W. E. Brumsickle, and R. D. Lorenz, "Control topology options for single-phase UPS inverters," *Industry Applications, IEEE Transactions* on, vol. 33, pp. 493-501, 1997.

- [2] J. Holtz and K. H. Werner, "Multi-inverter UPS system with redundant load sharing control," *Industrial Electronics, IEEE Transactions on*, vol. 37, pp. 506-513, 1990.

- [3] H. Han, X. Hou, J. Yang, J. Wu, M. Su, and J. M. Guerrero, "Review of power sharing control strategies for islanding operation of AC microgrids," Smart Grid IEEE Transactions on, vol. 7, pp. 200-215, 2016.

- Smart Grid, IEEE Transactions on, vol. 7, pp. 200-215, 2016.

[4] M. C. Chandorkar, D. M. Divan, and R. Adapa, "Control of parallel connected inverters in standalone AC supply systems," Industry Applications, IEEE Transactions on, vol. 29, pp. 136-143, 1993.

- [5] E. A. A. Coelho, P. C. Cortizo, and P. F. D. Garcia, "Small-signal stability for parallel-connected inverters in stand-alone AC supply systems," *Industry Applications, IEEE Transactions on*, vol. 38, pp. 533-542, 2002.

- [6] Z. Qing-Chang and G. Weiss, "Synchronverters: Inverters That Mimic Synchronous Generators," *Industrial Electronics, IEEE Transactions on*, vol. 58, pp. 1259-1267, 2011.

- [7] B. Johnson, S. Dhople, A. Hamadeh, and P. Krein, "Synchronization of Parallel Single-Phase Inverters With Virtual Oscillator Control," *Power Electronics, IEEE Transactions on*, vol. PP, pp. 1-1, 2014.

- [8] P. Kundur, N. J. Balu, and M. G. Lauby, Power system stability and control vol. 7: McGraw-hill New York, 1994.

- [9] Q. C. Zhong and Y. Zeng, "Universal Droop Control of Inverters With Different Types of Output Impedance," *IEEE Access*, vol. 4, pp. 702-712, 2016.

- [10] S. J. Chiang and J. M. Chang, "Parallel operation of series-connected PWM voltage regulators without control interconnection," *Electric Power Applications, IEE Proceedings* -, vol. 148, pp. 141-147, 2001.

- [11] J. M. Guerrero, L. Garcia de Vicuna, J. Matas, M. Castilla, and J. Miret, "Output Impedance Design of Parallel-Connected UPS Inverters With Wireless Load-Sharing Control," *Industrial Electronics, IEEE Transactions* on, vol. 52, pp. 1126-1135, 2005.

- [12] T. Yong, L. Quanwei, D. Yan, L. Xunhao, and H. Xiangning, "Analysis and Mitigation of Inverter Output Impedance Impacts for Distributed Energy Resource Interface," *Power Electronics, IEEE Transactions on*, vol. 30, pp. 3563-3576, 2015.

- [13] Z. Qing-Chang and D. Boroyevich, "A droop controller is intrinsically a phase-locked loop," in *Industrial Electronics Society, IECON 2013 - 39th Annual Conference of the IEEE*, 2013, pp. 5916-5921.

- [14] Y. Guan, J. M. Guerrero, X. Zhao, J. C. Vasquez, and X. Guo, "A New Way of Controlling Parallel-Connected Inverters by Using Synchronous-Reference-Frame Virtual Impedance Loop—Part I: Control Principle," *IEEE Transactions on Power Electronics*, vol. 31, pp. 4576-4593, 2016.

- [15] R. Majumder, A. Ghosh, G. Ledwich, and F. Zare, "Load sharing and power quality enhanced operation of a distributed microgrid," *Renewable Power Generation*, *IET*, vol. 3, pp. 109-119, 2009.

- [16] R. E. Carballo, F. Botterón, G. G. Oggier, and G. O. García, "Una metodología de diseño simple para controladores resonantes en tiempo discreto aplicados a UPS," presented at the XVI Reunión de Trabajo en Procesamiento de la Información y Control, Córdoba, Argentina, 2015.

- [17] P. Mattavelli, F. Paolo, F. Dal Lago, and S. Saggini, "Analysis of Control-Delay Reduction for the Improvement of UPS Voltage-Loop Bandwidth," *Industrial Electronics, IEEE Transactions on*, vol. 55, pp. 2903-2911, 2008

- [18] A. G. Yepes, F. D. Freijedo, J. Doval-Gandoy, O. Lopez, J. Malvar, and P. Fernandez-Comesaña, "Effects of Discretization Methods on the Performance of Resonant Controllers," Power Electronics, IEEE Transactions on, vol. 25, pp. 1692-1712, 2010.

- [19] Y. Yunhu, Z. Keliang, C. Ming, and Z. Bin, "Phase Compensation Multiresonant Control of CVCF PWM Converters," *Power Electronics*, *IEEE Transactions on*, vol. 28, pp. 3923-3930, 2013.

- [20] D. De and V. Ramanarayanan, "Decentralized Parallel Operation of Inverters Sharing Unbalanced and Nonlinear Loads," *Power Electronics*, *IEEE Transactions on*, vol. 25, pp. 3015-3025, 2010.

- [21] J. Liu, J. Yang, and Z. Wang, "A new approach for single-phase harmonic current detecting and its application in a hybrid active power filter," in *Industrial Electronics Society*, 1999. IECON'99 Proceedings. The 25th Annual Conference of the IEEE, 1999, pp. 849-854.

- [22] D. Dong, T. Thacker, R. Burgos, W. Fei, and D. Boroyevich, "On Zero Steady-State Error Voltage Control of Single-Phase PWM Inverters With Different Load Types," *Power Electronics, IEEE Transactions on*, vol. 26, pp. 3285-3297, 2011.

- [23] N. Pogaku, M. Prodanovic, and T. C. Green, "Modeling, Analysis and Testing of Autonomous Operation of an Inverter-Based Microgrid," *Power Electronics, IEEE Transactions on*, vol. 22, pp. 613-625, 2007.

- [24] T. B. Lazzarin, "Paralelismo de inversores de tensão," Phd., Universidade Federal de Santa Catarina, Florianópolis, 2010.